What is Traceformer?

製造後に設計ミスが発覚すると、多大なコストがかかり、数週間に及ぶ遅延や高額な基板の再設計(リスピン)を余儀なくされることがよくあります。標準的な電気ルールチェック(ERC)では基本的な配線エラーは検出できますが、データシートを「読解」して部品が正しく実装されているかを検証することはできません。

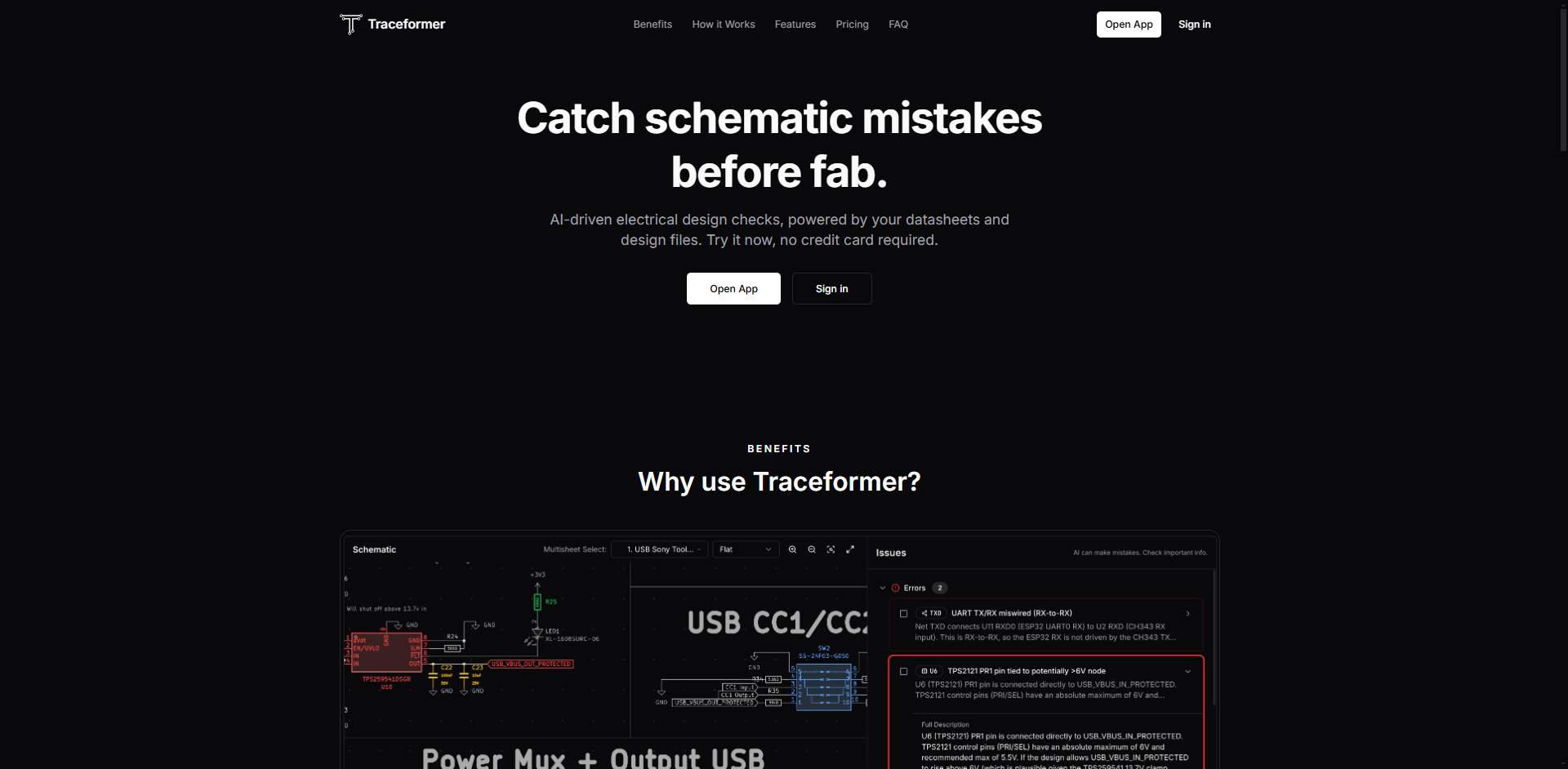

Traceformer.io はこのギャップを埋めます。これは自動化された設計レビューレイヤーとして機能し、KiCad プロジェクトや Altium のネットリストを、使用部品の実際の技術仕様と照らし合わせて分析します。マルチエージェント型AIパイプラインを活用することで、従来のソフトウェアでは見逃されがちな複雑なアプリケーションレベルのミスを特定します。

主な特長

- 🔍 マルチエージェント協調処理: システムは「計画(Planning)」「検索(Retrieval)」「統合(Synthesis)」の3段階パイプラインで動作します。「プランナー」エージェントが回路図を電源や通信などサブシステム単位に分割し、最大10個の「ワーカー」エージェントが並列でデータシートを分析し、各セクションの実装を検証します。

- 📑 自動データシート取得: PDFを手作業で収集する必要がなくなります。Traceformer は設計ファイルに基づき信頼できるソースから自動的にデータシートを取得し、AIによるレビューが常に使用部品の具体的な要件に基づいて行われることを保証します。

- ✅ 根拠に基づく指摘内容: 推測やAIによる幻覚(ハルシネーション)を排除するため、すべてのエラーや警告にはデータシートの該当ページからの直接引用が付与されます。これにより、フラグが立った理由を即座に確認し、適切な修正が行えます。

- ⚙️ 柔軟なレビュー設定: 分析の深さはユーザーがコントロールできます。特定の設計ルールを設定したり、トークン制限を調整したり、プロジェクトの複雑さに応じて OpenAI や Anthropic の異なるAIモデルを選択したりすることが可能です。

ユースケース

- サブシステム検証: 基板を製造に出す前に、Traceformer を使って電源供給ネットワークやSPI・I2Cなどの高速通信インターフェースが、メーカー資料に定義された電気的特性を厳密に満たしているかを検証できます。

- 最終的な「ケアレスミス」チェック: 標準ERCツールでは検出できない、TX/RXラインの入れ違いやプルアップ抵抗値の誤設定といった単純ながら致命的なミスを並列レビューで捕捉します。

- ドキュメントギャップ分析: AIが提供されたデータシート内に接続の妥当性を裏付ける十分な情報を見つけられない場合、「Missing Info(情報不足)」として分類します。これにより、設計が文書化された事実ではなく仮定に依存している箇所を明確に特定できます。

Traceformer がもたらすワークフローの進化

Traceformer の最大の価値は、文脈を理解した分析が可能である点にあります。従来のEDAツールは「2つのピンが接続されていること」は認識できますが、「なぜそのように接続されているのか」までは理解できません。一方、Traceformer は部品仕様書を読み解くことで回路の設計意図を把握します。

ネットリストと80ページにも及ぶデータシートを人力で照合する煩雑な作業を自動化することで、レビュー時の認知負荷を大幅に軽減します。これはエンジニアの専門知識を置き換えるものではなく、人手では到底達成不可能な規模と速度で高精度な「第二の目」として機能し、ファーストターンで正常動作する基板の実現可能性を高めます。

プロフェッショナル向け要約

Traceformer.io は、回路図レビューを手作業で行うミスの多い作業から、構造化されたAI支援型検証プロセスへと変革します。検証可能なデータシートの根拠に基づいた分析により、ハードウェアエンジニアは製造ラインに到達する前に複雑な設計欠陥を確実に捕捉できる信頼性の高い手法を手に入れます。