What is Traceformer?

一旦電路板完成製造後才發現設計錯誤,代價往往十分高昂,通常會造成數週的延誤,並需花費大量成本重新製作電路板。雖然標準的電氣規則檢查(ERC)能捕捉基本的佈線問題,卻無法「閱讀」元件規格書(datasheet),以驗證您的元件是否確實正確實作。

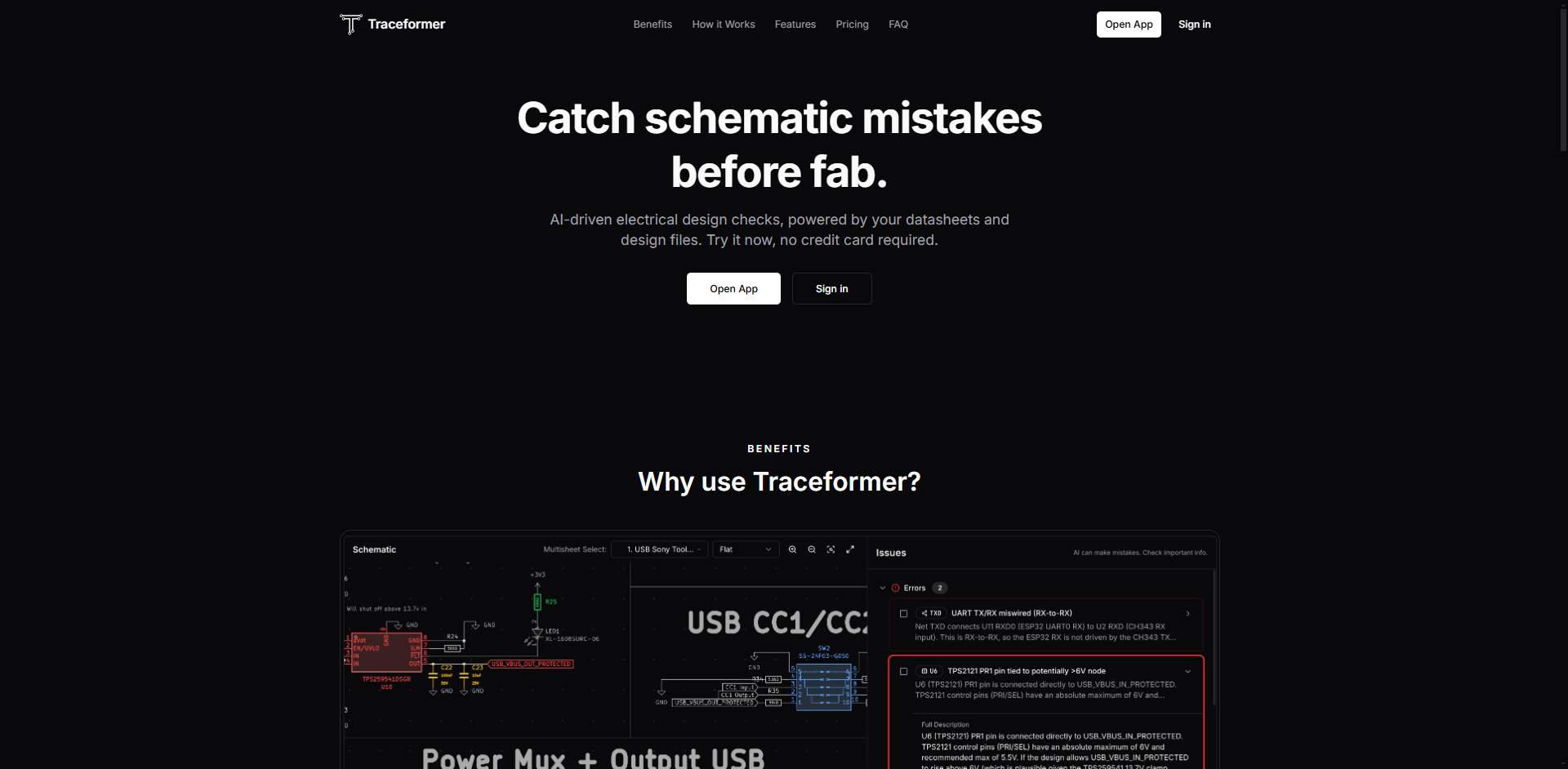

Traceformer.io 正是為彌補此一缺口而生。它作為一個自動化設計審查層,能將您的 KiCad 專案或 Altium 網表(netlist)與元件實際的技術規格進行比對分析。透過多智能體(multi-agent)AI 流水線技術,它能識別出傳統軟體所遺漏的複雜應用層級錯誤。

核心功能

- 🔍 多智能體協同運作:系統採用三階段流水線——規劃(Planning)、檢索(Retrieval)與合成(Synthesis)。其中「規劃者」(Planner)智能體會將您的電路圖拆解為多個子系統(例如電源或通訊模組),最多可同時啟動 10 個「工作者」(Worker)智能體,各自分析元件規格書,逐一驗證各子系統。

- 📑 自動化規格書擷取:您不再需要手動蒐集 PDF 檔案。Traceformer 能直接從您提供的設計檔案中,自動從可信賴來源抓取對應的元件規格書,確保 AI 審查始終基於您所選元件的具體技術要求。

- ✅ 基於證據的審查結果:為避免猜測與 AI 幻覺(hallucination),每項錯誤或警告皆附有直接引用自規格書特定頁面的明確佐證。這讓您能立即核實警示背後的依據,並做出有根據的修正。

- ⚙️ 可自訂的審查參數:您可完全掌控分析的深度。無論是設定特定設計規則、調整 token 上限,或選擇 OpenAI 與 Anthropic 提供的不同 AI 模型,皆可依專案複雜度靈活調整。

應用情境

- 子系統驗證:在送板至製造前,使用 Traceformer 驗證您的電源配送網路(PDN)與高速通訊介面(如 SPI 或 I2C)是否嚴格符合原廠文件所定義的電氣特性。

- 最終「非受迫性錯誤」掃描:執行平行審查,捕捉那些看似簡單卻可能造成嚴重後果的疏失——例如 TX/RX 訊號線接反,或上拉電阻值設定錯誤——這些都是標準 ERC 工具無法偵測的問題。

- 文件缺口分析:若 AI 在所提供的規格書中找不到足夠證據以驗證某個連接,便會將該檢查標記為「資訊不足」(Missing Info)。這能精準指出您的設計何處仰賴假設,而非確鑿的文件依據。

Traceformer 如何提升您的工作流程

Traceformer 的核心價值在於其具備情境理解能力。傳統 EDA 工具僅知道兩個接腳彼此相連,卻無法理解「為何如此連接」。而 Traceformer 則能透過閱讀元件規格,真正理解電路的設計意圖。

透過自動化處理繁瑣的網表與長達 80 頁規格書之間的交叉比對工作,大幅減輕工程師在審查過程中的認知負擔。這並非取代您的專業判斷,而是提供一套高保真度的「第二雙眼睛」,以人力難以企及的規模與速度進行審查,最終大幅提升首版電路板即能正常運作的成功機率。

專業總結

Traceformer.io 將原本耗時且易出錯的手動電路圖審查,轉化為結構化的 AI 輔助驗證流程。透過以可驗證的規格書證據為基礎進行分析,為硬體工程師提供一套可靠的方法,在設計進入生產線前即能揪出複雜的潛在缺陷。

More information on Traceformer

Launched

2025-12

Pricing Model

Freemium

Starting Price

$10 per month

Global Rank

Follow

Month Visit

<5k

Tech used